|

|

a) Design a synchronous 3-bit updown counter using J-K flip flops.

This question has 0 answers so far.

|

|

|

(b) Draw the logic diagram or POS Y = (x1+x2) (x2+x3)

Show the presence of hazard, its type and a way of removal.

This question has 0 answers so far.

|

|

|

(a) Write VHDL code for 4 bit asynchronous counter.

This question has 0 answers so far.

|

|

|

(c) Explain different types of standard logic.

This question has 0 answers so far.

|

|

|

(b) Explain the difference between concurrent and sequential signal assignment.

This question has 0 answers so far.

|

|

|

(a) Explain Generate statement with an example.

This question has 0 answers so far.

|

|

|

(b) Explain inertial and transport delay using example.

This question has 0 answers so far.

|

|

|

(a) Write down VHDL code for full adder using structural modeling.

This question has 0 answers so far.

|

|

|

5. Write short note on: b) SRAM and DRAM

This question has 0 answers so far.

|

|

|

5. Write short note on: a) CMOS Logic

This question has 0 answers so far.

|

|

|

b) Explain the working of flash type ADC.

This question has 0 answers so far.

|

|

|

(a) Write a test bench and VHDL code for 2 bit multiplier.

This question has 0 answers so far.

|

|

|

b) Draw the circuit diagram of master slave J-K flip flop and explain

its operation with the help of truth table.

This question has 0 answers so far.

|

|

|

a) Give the comparison between PROM, PLA and PAL.

This question has 0 answers so far.

|

|

|

b) Write short note on BCD to 7 segment decoder.

This question has 0 answers so far.

|

|

|

a) With the help of a logic diagram and truth table explain an octal to

binary encoder.

This question has 0 answers so far.

|

|

|

b) Implement the following function with a MUX F(a,b,c)= m(1,3,5,6) Take 'a' and 'b' as select inputs. m(1,3,5,6) Take 'a' and 'b' as select inputs.

This question has 0 answers so far.

|

|

|

a) Draw the logic diagram of 4-bit binary parallel adder and explain

operation.

This question has 0 answers so far.

|

|

|

b)Make a k-map of the following expression and obtain the minimal

of SOP and POS forms

This question has 0 answers so far.

|

|

|

a) Reduce the following expression using k-map and implement the

minimal expression in universal logic. F= m(0,2,4,6,7,8,10,12,13,15) m(0,2,4,6,7,8,10,12,13,15)

This question has 0 answers so far.

|

|

|

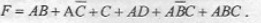

b) Draw the logic diagram using only two input NAND gates to

implement the following expression.

This question has 0 answers so far.

|

|

|

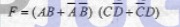

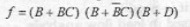

a) Reduce the expression

This question has 0 answers so far.

|

|

|

c) Explain critical and non-critical race.

This question has 0 answers so far.

|

|

|

Write VHDL code for (c) Serial in parallel out shift register.

This question has 0 answers so far.

|

|

|

Write VHDL code for (b) 4x16 decoder

This question has 0 answers so far.

|

|

|

Write VHDL code for (a) SR flip flop

This question has 0 answers so far.

|

|

|

j) What is signature?

This question has 0 answers so far.

|

|

|

(i) Define test bench.

This question has 0 answers so far.

|

|

|

(h) What is overloading in VHDL?

This question has 0 answers so far.

|

|

|

(g) What are the capabilities of VHDL?

This question has 0 answers so far.

|

|

|

(f) What are ASM charts?

This question has 0 answers so far.

|

|

|

(e) How does a PLA differ from PAL?

This question has 0 answers so far.

|

|

|

(d) Give difference between Mealy and Moore model.

This question has 0 answers so far.

|

|

|

f) Write the different application of 555 timer.

This question has 0 answers so far.

|

|

|

(b) Define wait statement.

This question has 0 answers so far.

|

|

|

(a) What are generics?

This question has 0 answers so far.

|

|

|

(b) What is altera's cyclone processor? Explain using any example.

This question has 0 answers so far.

|

|

|

(a) Define FPGA and its use in industry.

This question has 0 answers so far.

|

|

|

(b) Describe block diagram of any Xilinx series.

This question has 0 answers so far.

|

|

|

(a) Define CPLD and give its applications.

This question has 0 answers so far.

|

|

|

(b) Draw state machine model for the sequence 1010 and write VHDL code for that.

This question has 0 answers so far.

|

|

|

(a) Which command is used for dumping results into a text file? Explain with example.

This question has 0 answers so far.

|

|

|

(b) What are pure and impure functions? Give difference between functions and procedures.

This question has 0 answers so far.

|

|

|

Simplify the following Boolean expression using Karnaugh maps:

F(A,B,C,D) = {(3, 7, 11, 13, 14, 15).

This question has 0 answers so far.

|

|

|

Compare Linear-ramp ADC and Dual-slope ADC.

This question has 0 answers so far.

|

|

|

Describe the functioning of R-2R Ladder D/A Converter.

This question has 0 answers so far.

|

|

|

Draw the state diagram for sequence detector of D flip-flop.

This question has 0 answers so far.

|

|

|

Compare flip-flop excitation table and characteristics table. Draw the flip-flop excitation table of RS flip-flop.

This question has 0 answers so far.

|

|

|

Draw the logic diagram of a four-bit binary ripple countdown counter using flip-flops that trigger on the positive edge of the clock.

This question has 0 answers so far.

|

|

|

Explain the features of Monostable Multivibrator.

This question has 0 answers so far.

|

|

|

Design a four-bit binary synchronous counter using D flip-flops.

This question has 0 answers so far.

|

|

|

Explain race-around condition in JK flip flop. Draw the sequential circuit of JK flip flop and give its state table.

This question has 0 answers so far.

|

|

|

Give the illustration of BCD-to Decimal Decoder.

This question has 0 answers so far.

|

|

|

Draw the block diagram of a 4-to 1-line multiplexer. Explain its operations by means of a function table.

This question has 0 answers so far.

|

|

|

Explain three different types of output configurations in TTL gates.

This question has 0 answers so far.

|

|

|

Construct a 4-to-16-line decoder using five 2-to-4-line decoders with enable.

This question has 0 answers so far.

|

|

|

Explain AND-OR-INVERT implementation with an illustration.

This question has 0 answers so far.

|

|

|

Draw the circuit diagram and truth table of full adder.

This question has 0 answers so far.

|

|

|

Explain the role of 555 timer and its application as as table multi-vibrator.

This question has 0 answers so far.

|

|

|

Draw the circuit of full subtractor.

This question has 0 answers so far.

|

|

|

Give an illustration of comparator.

This question has 0 answers so far.

|

|

|

Mention the features of configurable Programmable Array Logic.

This question has 0 answers so far.

|

|

|

Explain bipolar transistor characteristics.

This question has 0 answers so far.

|

|

|

Explain various types of ROMs.

This question has 0 answers so far.

|

|

|

Give the block diagram and timing diagram of serial transfer from register A to register B.

This question has 0 answers so far.

|

|

|

Explain the functioning of Programmable Logic Array AND matrix and OR matrix

This question has 0 answers so far.

|

|

|

e) Compare between combinational and sequential circuits.

This question has 0 answers so far.

|

|

|

d) Design a 32:1 multiplexer using 16:1 mux and 2:1 multiplexer.

This question has 0 answers so far.

|

|

|

c) Show that NAND and NOR gates are universal gates.

This question has 0 answers so far.

|

|

|

b) What are asynchronous sequential circuits?

This question has 0 answers so far.

|

|

|

a) What are analog circuits? Give a few examples.

This question has 0 answers so far.

|

|

|

Compare PAL and PLA.

This question has 0 answers so far.

|

|

|

Draw PLA circuit to implement the functions:

F2 = (AC + AB + BC)'

This question has 0 answers so far.

|

|

|

Draw PLA circuit to implement the functions:

F1 = A'B + AC' + A'BC'

This question has 0 answers so far.

|

|

|

Explain the functioning of Programmable Logic Array Expanding PLA capacity.

This question has 0 answers so far.

|

|

|

Explain the functioning of Programmable Logic Array Output through FLIP-FIOPs and Buffers.

This question has 0 answers so far.

|

|

|

Explain the functioning of Binary-weighed DAC using a neat diagram.

This question has 0 answers so far.

|

|

|

How many lines must be decoded for the chip select inputs?Specify the size of the decoder.

This question has 0 answers so far.

|

|

|

How many lines of the address must be used to access 256 K bytes? How many of these lines are connected to the address input of all chips?

This question has 0 answers so far.

|

|

|

How many 32 K X 8 RAM chips are needed to provide a memory

capacity of 256 K bytes?

This question has 0 answers so far.

|

|

|

Explain the functional aspects of content addressable memory.

This question has 0 answers so far.

|

|

|

Explain the Mode of memory access.

This question has 0 answers so far.

|

|

|

Explain the Physical characteristics of memory.

This question has 0 answers so far.

|

|

|

Explain the operational Diode Transistor Logic (DTL) using NAND Gate. Derive the expression for propagation delay.

This question has 0 answers so far.

|

|

|

Give an example to illustrate binary-weighted DAC.

This question has 0 answers so far.

|

|

|

Explain CMOS characteristics.

This question has 0 answers so far.

|